0 ����

�I�B�����W��ע����ȫ���|Samtec�B�����F؛�������YԴ���LJ����I�ȵ�TE��̩����ӣ�TYCO����Molex��Ī�ˣ���JAE��JST��FCI��Samtec����̩����Amphenol�����M�Z���B������ُ����ƽ�_���p�ɝM�������B������ُ����

�����꣬�S��������M�aƷ������������L������MOSFET������ҲԽ��Խ�����У�TMOS���ڜϵ��Ǵ�ֱ��������ͬ��e�£���λԪ���ļ��ɶ��^�ߣ���ˌ�ͨ����^�ͣ�ͬ�r�־����^�͵Ėţ�©늺��ܶȡ��^�������������Ķ��߂����^�͵��_�P�p�ļ��^����_�P�ٶȣ����V���ؑ����ڵ͉������I��

�͉�TMOS�Č�ͨ�����Ҫ���ɜϵ��������ӌ�������M�ɣ����˽��͌�ͨ��裬ͬ�r�����������������ܣ���©Դ����늉�����ֱ�ӵ��k���ǜp������Ԫ�����g�࣬����ͬ����e�£�����Ԫ���ļ��ɶȡ����ڴˣ����Ľ����˜ϲ�ʽ���|�����Լ�ͻ��ʽ�ྦྷ��Y�����˷��ɳߴ�sС���l�Ĝϵ���ͨЧ������Kͨ�^ԇ�ɹ��_�l���ŘO늉���4.5 V���������5 A�r��Rdson·A��9.5 mΩ·mm2��©Դ����늉�����20 V���_��늉�0.7 V��Ԫ���g��1.4μm��n��TMOS��

1 ���������c��ˇ���F

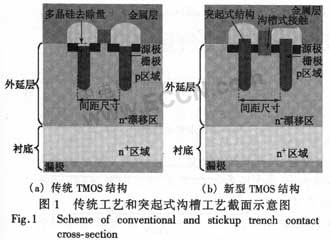

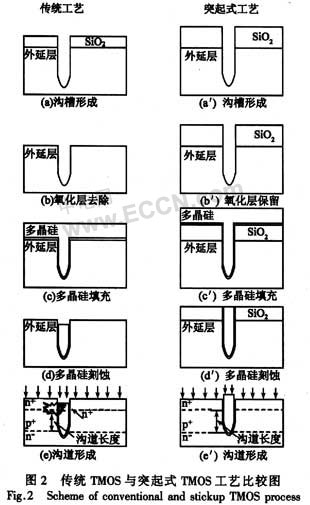

ͨ�^�D1�Ђ��yTMOS�Ľ���D��ͻ��ʽ�ϲ۹�ˇ����D�ı��^�����Կ������y�Ĺ�ˇ�����ù�̹�ˇ����ģ���γ�����Դ�^(n+)�����Ǯ��ߴ粻��sС�Ժ�Դ�^��ģ���γɵĹ���z�ߴ��S֮׃С���ں��m���x��ע�빤ˇ�У������˹���zÓ����L�U���@����ζ����λԪ���б�ԓ������z�ڱε���Դ�^����ע��As+�x�ӣ��Ķ��a��������npn���O�ܣ��������������r©����ӣ�������r������������ȫʧЧ�����IJ��Üϲ�ʽ���|�@һ�����Դ�^ע��r����Դ�^����������z��As+�x����ȫע�룬֮�����ý��|����ģ��ֱ�ӿ��g�������As+�x��ע��^����ȫ�����˂��y��ˇ�®a������npn���O�ܵ��L�U����

����λԪ�������g����1.4 μm��ˇ�r�������OӋ�Ĝϵ��L�ȴ�s��0.5μm��Դ�^�Y�����0.3μm�����ò����]�����y��ˇ��Դ�^ע��r���ྦྷ����g��ˇ���������������������½����L�U���ڂ��y��ˇ�У����ྦྷ����e��ɺ��ͨ�^���g���γɖŘO�^���Ƕྦྷ��ȥ�����y�Ծ��ʿ��ƣ�ͬ�r���]�����g��ˇ��Ⱦ����Ե����c��SiƬ�������c߅����ȥ�����o�����C��ͬ���Ķ����S���Դ�^ע�˹�ˇ�����˝��ڵ��L�U������Դ�^ע��r������ŘO�ྦྷ����g���^�࣬������Դ�^�ߝ�ȵ�As+�x�ӏĖŘO߅��ע�뵽�ϵ��У��g�ӵp���˜ϵ��L�ȣ��Ķ��������ֵ�_��늉�(Vth)�����䮔�ϵ��L���^�̕r����������������������������B�r�l��©Դ�g��ͨЧ������K��������ʧЧ�����IJ���K·Shenai��ͻ��ʽ�Y�������γɜϲ�֮���ȱ���֮ǰ�����L�������ӣ�Ȼ��ֱ�����L�ŘO����Ĥ�Ͷྦྷ�裬�ږŘO�ྦྷ���γɺŌ���ǰ���L��������ȥ�����ɴ˱��γ���ͻ��ʽ�ྦྷ��Y�����Ķ����Ա��C���S���Դ�^As+�x��ע��r��As+�x�ӟo���Ĝϲۂȱ�ע�뵽�ϵ��У��ĸ����ϱ����˰l��Դ©�O֮�g��ͨ�Ŀ����ԣ����������������g��ˇ����ه�̶ȡ��@�c�������ŘO����Ĥ����^������r���������@���˕r������Â��y��ˇ��Դ�^�x��ע��r��As+�x�Ӹ����Ăȱ�ע�뵽�ϵ��У��Ķ�Ӱ표ϵ��L�ȡ�

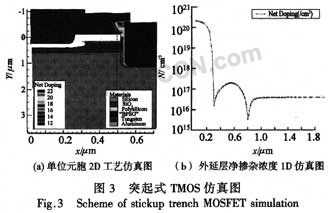

����ͨ�^�C���\�Üϲ�ʽ���|�Լ�ͻ��ʽ�Y���@�ɂ����g���õ���©Դ�g����늉�����20 V���ֵ�_��늉�0.7 V���ŘO����늉�����12 V�Լ��ږŘO늉�4.5 v���������5 A�r��ͨ���Rdson·A��9.5 mΩ·mm2��n��TMOS���D3���\��SILVACO��˾��Athena��ˇ����ܛ����ģ�M�����������Y��ʾ��D�Լ����ӌ��еă����s�x�ӝ�����������Կ������ϵ��L�ȴ���0.5μm��Դ�^�Y���0.3μm��

2�Y���cӑՓ

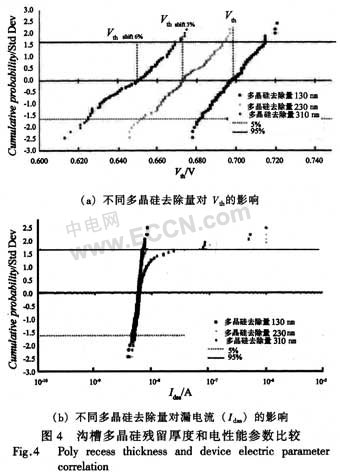

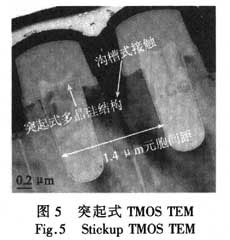

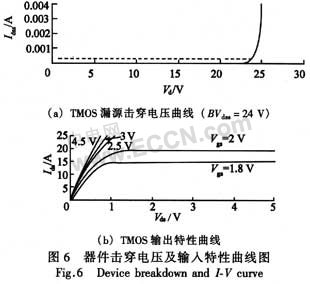

������C�@һ��Փ���e�OӋ���ڂ��y��ˇ�£��ŘO픲������ӌӱ���Ķྦྷ��ȥ����(130 nm��230 nm��310 nm)��ԇͨ�^����������܅������^�������Կ������S���ྦྷ��ȥ���������ӣ��ֵ�_��늉��S֮���ͣ��f���������ϵ���Ч�L��׃�̣�Դ�^�x��ͨ�^�ȱ�ע�뵽�ϵ��У�Դ�^�Y���ڜϵ�����׃�ͬ�r�ɈD4(b)��֪��©Դ�g©���Ҳ�����@�ą^�e�����ྦྷ��ȥ������310 nm�r�����۷e���ʈD�п��Կ����в��օ^��©��������@һ�F���S���ྦྷ��ȥ�����Ĝp�ٶ�����ʧ���Ķ���C�˜ϵ���Ч�L���c�ྦྷ��ȥ�����к������P�ԡ��ɴ˿�Ҋ�����˜p�����������c���g��ˇ�����P�ԣ�����ͻ��ʽ�ྦྷ�輼�g�Ƿdz���Ҫ�ġ��D5�Dz���������@�R���õ���ͻ��ʽTMOS���H����D�����Կ�����ԓ�D�е�ͻ��ʽ�ྦྷ��Y���Լ��ϲ�ʽ���|����λԪ�������g����1.4μm��n��TMOS����оƬ��Դ�^��e��0.4 nm2��������TSOP6���b���D6(a)��(b)�քe����������늉������Լ�ݔ�������������ɈD6(a)���Կ�������©��©�����250μA�r������늉���24 V���M�����20 V���OӋ��Ҫ���ɈD6(b)���Կ��������ŘO�_��늉���4.5 v�����������5 A�r�������Č�ͨ������23.75 mΩ������оƬ��Դ�^�OӋ�ߴ��0.4 mm2����KRdson·A��9.5 mΩ·mm2

3 �Y�Z

��������λԪ���ߴ粻��sС���������OӋ�ŘO����Ĥ�^���������r���ڂ��y��TMOS��ˇ�У�Դ�^ע������ŘO�ȱ�Ӱ��������ܡ�����ͻ��ʽ�Y��������Ч�ر�����g��ˇ��Դ�^ע�댦�^�̜ϵ��������g��Ӱ푣�������������ͨ���L�U�����C�������ķ������ܺͿ��؏��ԡ�

Samtec�پW�������|����Ϣ�YԴ���ИI�YӍ�������_�l�������YӍ��Ϣƽ�_��